# A Novel Step-Up Multilevel Inverter

# NIRAJ KUMAR DEWANGAN<sup>1</sup>, KRISHNA KUMAR GUPTA<sup>2</sup>, PALLAVEE BHATNAGAR<sup>3</sup> <sup>1, 2, 3</sup> Sagar Institute of Science and Technology, Bhopal, MP, India

Abstract- Switched-capacitors based multilevel inverters are of two types: single-stage and two-stage. Two-stage topologies require four polarity-reversing switches of high blocking-voltage. A single-stage topology is proposed in this work which can synthesize thirteen levels with a single input source and three capacitors, with an overall voltage gain of three. The proposed inverter uses fourteen power switches, of which the blocking-voltage of ten switches are restricted to the source voltage. The remaining four switches have blocking-voltage equal to twice the source voltage and they operate at low frequency. Thus, for all switches, the blockingvoltage is less than the peak output voltage. The proposed module is validated experimentally and results are presented in this paper. A comparison of the proposed topology with other similar topologies is also presented.

Indexed Terms- Multilevel inverter, switchedcapacitors, blocking-voltage

#### I. INTRODUCTION

RELIANCE on conventional fuels for energy needs of the world is being actively reduced due to concerns over pollution and price fluctuations [1]. As a result, vehicular electrification is being promoted and electric vehicles (EVs), hybrid cars, fuel cell vehicles etc. are penetrating the automobile market. Similarly, electric power production by using photovoltaic (PV) source is gaining significant grounds. For EV and PV applications, the input power source is of low dc voltage and the output ac waveform is required to fulfill stringent norms in terms of waveform quality. Switched-capacitors based multilevel inverters (SCMLIs) have been introduced to obtain a high quality stepped-up multilevel ac waveform from a dc source of lesser voltage [2]. MLIs also offer other benefits too such as: blocking-voltage of power switches is less (as compared to the magnitude of the output, generally referred to as the 'operating voltage'), reduced filtering requirements, much reduced dv/dt variation experienced by the load etc. [3]. SCMLIs enable the voltage-gain to be greater than unity with the use of switched capacitors [4,5]. Numerous SCMLI topologies have recently proposed [2-15]. The SCMLI modules presented in [2, 7, 9, 12] feature self-balanced capacitors but have high component count, while the SCMLI structures discussed in [3, 6, 10, 11] require power switches with high blocking-voltage capability. The topology presented in [14] requires a complex closed loop control scheme to balance the capacitor voltage. The topology presented in [5] is a two-stage structure with H-bridge switches having large blocking-voltage requirements. In this work, a single stage SCMLI topology is presented with following features: (a) voltage gain per module is three; (b) thirteen-level waveform is generated using one dc source, three capacitors and fourteen power switches, with no requirement of additional diodes; (c) all capacitors are self-balanced; (d) blocking-voltages of all power switches are significantly less than the operating voltage; and (e) the two power switches with clockingvoltage equal to two-times the input voltage, can be operated at line frequency, thereby minimizing the switching losses. The remaining paper is as follows: the proposed topology is explained in section II, along with a comparison with other topologies. A switching methodology is discussed in section III. Experimental results are presented in section IV for validation, while conclusions are discussed in section V.

## II. PROPOSED THIRTEEN-LEVEL INVERTER

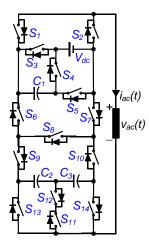

The structure of the proposed thirteen-level inverter is shown in Fig. 1 and it consists of fourteen power switches  $S_j$  {j = 1 to 14}, three capacitors ( $C_1$ ,  $C_2$  and  $C_3$ ) and one dc source ( $V_{dc}$ ). The output ac voltage is marked as ' $v_{ac}(t)$ '. Voltage of capacitor  $C_1$  is to be maintained at  $V_{dc}$ , while voltages of capacitors  $C_2$  and  $C_3$  are to be maintained at  $0.5V_{dc}$  each.

Fig.1. Proposed 3X-voltage-gain 13-level switched capacitor inverter

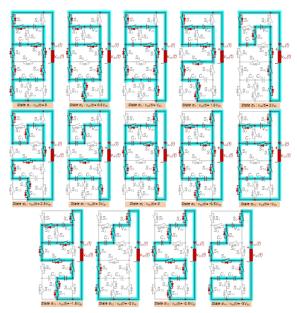

Fig.2. Working states for the proposed thirteen-level inverter with switched capacitors

For the proposed inverter, the blocking-voltage requirements for the power switches are shown in Table I.

| TABLE I                                              |  |  |  |  |  |

|------------------------------------------------------|--|--|--|--|--|

| BLOCKING-VOLTAGE OF POWER SWITCHES IN THE            |  |  |  |  |  |

| PROPOSED INVERTER WITH $V_{\rm DC}$ as input voltage |  |  |  |  |  |

| AND $3V_{DC}$ as peak output                         |  |  |  |  |  |

| Blocking Voltage | Power Switches                                    |

|------------------|---------------------------------------------------|

| $0.5 V_{dc}$     | $S_{11}, S_{12}$                                  |

| $V_{dc}$         | $S_3, S_4, S_5, S_8, S_9, S_{10}, S_{13}, S_{14}$ |

| $2V_{dc}$        | $S_1, S_2, S_6, S_7$                              |

All the valid operating states  $\sigma_j$  {j = 1 to 14} for the proposed inverter are summarized in Fig.2. In states  $\sigma_1$ ,  $\sigma_2$ ,  $\sigma_3$ ,  $\sigma_4$ ,  $\sigma_8$ ,  $\sigma_9$ ,  $\sigma_{10}$  and  $\sigma_{11}$ ,  $C_1$  comes in parallel with  $V_{dc}$  and keep it self-balanced. Similarly,  $C_2$  and  $C_3$  combined come in parallel with  $V_{dc}$  during the states  $\sigma_1$ ,  $\sigma_2$ ,  $\sigma_3$ ,  $\sigma_8$ ,  $\sigma_9$  and  $\sigma_{10}$ . It can be seen that both the states  $\sigma_1$  and  $\sigma_8$  synthesize zero voltage at the output terminals. A judicious use of states can help in operating the switches  $S_1$  and  $S_2$  at a frequency equal to the line frequency. For this, zero voltage levels in the positive and negative halves should be obtained by using states  $\sigma_1$  and  $\sigma_8$  respectively. A procedure to attain the same is described in section III.

As far as the classical multilevel topologies (viz. diode-clamped, flying capacitors and cascaded Hbridge) are concerned, the voltage gain is unity, whereas, the switched capacitors-based structures offer a voltage gain greater than unity. Hence, an appropriate comparison of the proposed topology would be with other switched capacitors-based structures. In Table II, a comparison of the proposed inverter with other SCMLIs is presented considering the requirement of components. In Table III, the comparison is extended with the consideration of blocking-voltage (BV) and total-blocking-voltage (TBV) requirements, as these factors greatly determine the cost and application of the topologies [17,18]. Since the topologies being considered for comparison have different number of levels in the output, the number of components per output level is also shown Table II in its ninth column and it can be observed that the proposed inverter requires minimal components per level. It can also be observed from Table II and Table III that topologies presented in [3, 6, 7, 10, 11] require power switches with large BVs. whereas the TBV is significantly high for the topologies presented in [5, 6, 7, 11, 12]. It should also be noted that the proposed topology is highly competent in terms of the total standing voltage and overall component count of 3.384 per level. Though topology presented in [16] is more advantageous in terms of TBV and BV, it requires more components as compared to the proposed module.

#### TABLE II

# © OCT 2017 | IRE Journals | Volume 1 Issue 4 | ISSN: 2456-8880

COMPARISON OF THE PROPOSED TOPOLOGY WITH OTHER SWITCHED CAPACITORS BASED TOPOLOGIES  $(N_L = \text{NUMBER OF OUTPUT LEVELS}, N_{IS} = \text{NUMBER OF}$ INPUT SOURCES,  $N_S = \text{NUMBER OF POWER SWITCHES},$  $N_D = \text{NUMBER OF MAIN DIODES}, N_{AD} = \text{NUMBER OF}$ AUXILIARY DIODES,  $N_{GD} = \text{NUMBER OF GATE DRIVERS},$  $N_C = \text{NUMBER OF CAPACITORS}$

|           |       |          |       |       |          |          |       | Component |

|-----------|-------|----------|-------|-------|----------|----------|-------|-----------|

| Reference | $N_L$ | $N_{IS}$ | $N_S$ | $N_D$ | $N_{AD}$ | $N_{GD}$ | $N_C$ | count per |

|           |       |          |       |       |          |          |       | level     |

| [2]       | 5     | 1        | 9     | 9     | 0        | 9        | 1     | 5.600     |

| [3]       | 9     | 1        | 10    | 10    | 1        | 8        | 2     | 3.444     |

| [4]       | 9     | 1        | 12    | 12    | 0        | 11       | 2     | 4.111     |

| [5]       | 7     | 1        | 10    | 10    | 0        | 10       | 2     | 4.571     |

| [6]       | 5     | 1        | 6     | 6     | 2        | 6        | 1     | 4.200     |

| [7]       | 7     | 1        | 16    | 16    | 0        | 14       | 2     | 6.857     |

| [8]       | 5     | 1        | 6     | 6     | 2        | 6        | 2     | 4.400     |

| [9]       | 5     | 1        | 9     | 9     | 1        | 8        | 1     | 5.600     |

| [10]      | 5     | 1        | 6     | 6     | 1        | 6        | 1     | 5.000     |

| [11]      | 5     | 2        | 8     | 8     | 0        | 8        | 0     | 4.800     |

| [12]      | 5     | 1        | 12    | 12    | 0        | 12       | 2     | 7.600     |

| [13]      | 5     | 1        | 7     | 7     | 3        | 7        | 2     | 5.200     |

| [16]      | 9     | 1        | 11    | 11    | 0        | 10       | 2     | 3.777     |

| Proposed  | 13    | 1        | 14    | 14    | 0        | 13       | 3     | 3.384     |

## TABLE III COMPARISON OF THE PROPOSED TOPOLOGY WITH OTHER SWITCHED CAPACITORS TOPOLOGIES IN TERMS OF TOTAL BLOCKING VOLTAGE (TBV) AND BLOCKING VOLTAGE (BV) REQUIREMENTS FOR AN INPUT DC

VOLT OF U

| VOLTAGE $V_{IN}$ |       |            |           |               |                 |  |  |

|------------------|-------|------------|-----------|---------------|-----------------|--|--|

|                  |       |            |           | TBV           | BV per<br>level |  |  |

|                  |       |            |           | per           |                 |  |  |

|                  |       |            |           | level         | in <i>per</i>   |  |  |

| Reference        | $N_L$ | TBV        | BV        | in <i>per</i> | unit            |  |  |

|                  |       |            |           | unit          | w.r.t.          |  |  |

|                  |       |            |           | w.r.t.        | $V_{in}$        |  |  |

|                  |       |            |           | $V_{in}$      |                 |  |  |

| [2]              | 5     | $9V_{in}$  | $V_{in}$  | 1.800         | 0.200           |  |  |

| [3]              | 5     | $11V_{in}$ | $2V_{in}$ | 2.200         | 2.200           |  |  |

| [4]              | 9     | $11V_{in}$ | $V_{in}$  | 1.222         | 0.111           |  |  |

| [5]              | 7     | $18V_{in}$ | $3V_{in}$ | 2.571         | 0.428           |  |  |

| [6]              | 5     | $12V_{in}$ | $2V_{in}$ | 2.400         | 0.400           |  |  |

| [7]              | 7     | $16V_{in}$ | $2V_{in}$ | 2.285         | 0.285           |  |  |

| [8]              | 5     | $8V_{in}$  | $V_{in}$  | 1.600         | 0.200           |  |  |

| [9]              | 5     | $9V_{in}$  | $V_{in}$  | 1.800         | 0.200           |  |  |

| [10]             | 5     | $11V_{in}$ | $2V_{in}$ | 2.200         | 0.400           |  |  |

| [11]             | 5     | $12V_{in}$ | $2V_{in}$ | 2.400         | 0.400           |  |  |

| [11]             | 5     | $12V_{in}$ | $2V_{in}$ | 2.400         | 0.400           |  |  |

| [12]     | 5  | $20V_{in}$ | $V_{in}$  | 4.000 | 0.200 |

|----------|----|------------|-----------|-------|-------|

| [13]     | 5  | $9V_{in}$  | $V_{in}$  | 1.800 | 0.200 |

| [16]     | 9  | $10V_{in}$ | $V_{in}$  | 1.111 | 0.111 |

| Proposed | 13 | $17V_{in}$ | $2V_{in}$ | 1.307 | 0.153 |

#### III. SWITCHING METHODOLOGY

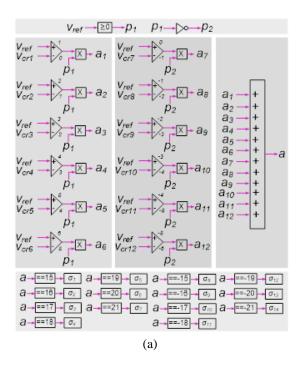

While the proposed topology can be modulated with any of the schemes for multilevel inverters with suitable adaptation, the multicarrier PWM scheme as described in [19] is used in this work as it felicitates the utilization of both the zero states. The scheme is shown in Fig. 3(a). Twelve triangular waveforms  $V_{cri}$  $\{j = 1 \text{ to } 12\}$  of 100Hz frequency each are used as carriers and are configured in phase opposition disposition. A sinusoidal waveform Vref of 50 Hz frequency is taken as the reference signal. These reference and carrier signals are shown in Fig. 3(b). A continuous comparison of the reference with the carriers is carried out. If the reference  $V_{ref}$  is greater than carriers, the comparators give 1, 2, 3, 4, 5, 6, 0, -1, -2, -3, -4 and -5 respectively for carriers  $V_{crj}$  {j = 1to 12}. On the other hand, if the reference  $V_{ref}$  is less than carriers, then comparators give respective outputs as 0, 1, 2, 3, 4, 5, -1, -2, -3, -4, -5 and -6. Signals  $a_i$  { j = 1 to 12} are added so as to obtain an aggregated signal 'a', shown in Fig. 3(c).

Fig.3. (a) switching scheme for the proposed module;(b) reference and carrier signals; and (c) aggregated signal 'a'

Aggregated signal 'a' has seven positive levels from 15 to 21 in steps of 1 and seven negative levels from - 15 to -21 in steps of -1. A one-to-one relationship of these levels in the output waveform is utilized to extract switching pulses (for the specific working states) as shown in Fig. 3(a).

### IV. EXPERIMENTAL VERIFICATION

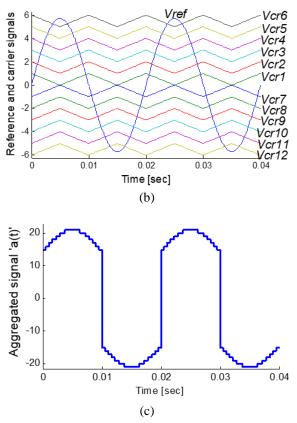

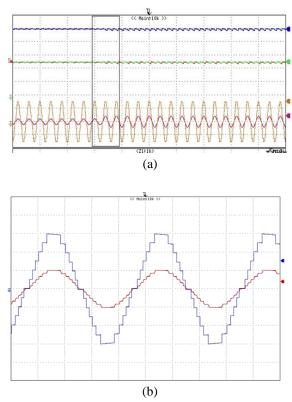

To validate the proposed topology, a laboratory set-up was made using discrete power switch modules (with MOSFETs IRF460 with suitable gate drivers). The input voltage was set to 100V and three capacitors of 2200µF each were used as  $C_1$ ,  $C_2$  and  $C_3$ . dSPACE DS1103 was used to generate real time gate signals. Carrier signals of 100 Hz and reference signal of 50 Hz was used with a modulation index of 0.95. The experimental waveforms are shown in Fig. 4 for an inductive load. The capacitors  $C_1$ ,  $C_2$  and  $C_3$  are self-balanced at their respective voltages of 100V, 50V and 50V, even when the load current is doubled. The

output waveform is a thirteen-level waveform in steps of 50V as expected. Thus, validity of the proposed structure is confirmed in terms of its working and capability of capacitors to be self-balanced.

Fig.4. Experimental results: (a) Voltages of capacitors  $C_1$ ,  $C_2$  and  $C_3$ , load voltage and load current; and (b) zoomed waveforms of load voltage and load current

#### CONCLUSION

A thirteen-level inverter with three-time voltage boosting capability is presented in this paper. The switched capacitors used in the topology are selfbalanced and the PIV of all the power switches are significantly less as compared to the operating voltage. A comparative study of the proposed topology with the contemporary topologies indicates its merit in terms of component count and total standing voltage. Experimental results validate the proposed structure. The proposed module can be used for applications which involve low voltage dc sources as input while requiring a high-resolution ac waveform with increased voltage as output.

## REFERENCES

- D. Abbott, "Keeping the Energy Debate Clean: How Do We Supply the World's Energy Needs?," *Proc. IEEE*,vol. 98, no. 1, pp. 42-66, Jan. 2010.

- M. Kanimozhi and P. Geetha, "A new boost switched capacitor multilevel inverter using different multi carrier PWM techniques," 2014 International Conference on Circuits, Power and Computing Technologies [ICCPCT-2014], 2014, pp. 432-437, doi: 10.1109/ICCPCT.2014.7054905.

- [3] M. S. W. Chan and K. T. Chau, "A New Switched-Capacitor Boost-Multilevel Inverter Using Partial Charging," in *IEEE Transactions* on Circuits and Systems II: Express Briefs, vol. 54, no. 12, pp. 1145-1149, Dec. 2007, doi: 10.1109/TCSII.2007.905352.

- [4] S. S. Lee, "Single-Stage Switched-Capacitor Module (S<sup>3</sup>CM) Topology for Cascaded Multilevel Inverter," *IEEE Trans. Power Electron.*,vol. 33, no. 10, pp. 8204-8207, Oct. 2016.

- [5] Y. Hinago and H. Koizumi, "A switchedcapacitor inverter using series/parallel conversion with inductive load," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 878-887, Feb. 2012.

- [6] Y. Ye, K. W. E. Cheng, J. Liu and K. Ding, "A step-up switched capacitor multilevel inverter with self-voltage balancing," *IEEE Trans. Ind. Electron.*, vol. 61, no. 12, pp. 6672-6680, Dec. 2014.

- [7] X. Sun, B. Wang, Y. Zhou, W. Wang, H. Du and Z. Lu, "A single dc source cascaded seven-level inverter integrating switched-capacitor techniques," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 7184-7194, Nov. 2016.

- [8] M. Saeedian, S. M. Hosseini and J. Adabi, "Stepup switched-capacitor module for cascaded MLI topologies," *IET Power Electron.*, vol. 11, no. 7, pp. 1286-1296, 2016.

- [9] E. Babaei and F. Sedaghati, "Series-parallel switched-capacitor based multilevel inverter," 2011 International Conference on

*Electrical Machines and Systems*, 2011, pp. 1-5, doi: 10.1109/ICEMS.2011.6073330.

- [10] R. Barzegarkhoo, H. M. Kojabadi, E. Zamiry, N. Vosoughi and L. Chang, "Generalized structure for a single phase switched-capacitor multilevel inverter using a new multiple dc link producer with reduced number of switches," *IEEE Trans. Power Electron.*, vol. 31, no. 8, pp. 5604-5617, Aug. 2016.

- [11] D. A. Ruiz-Caballero, R. M. Ramos-Astudillo, S. A. Mussa and M. L. Heldwein, "Symmetrical hybrid multilevel dc/ac converters with reduced number of insulated dc supplies," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2307-2314, July 2010.

- [12] L. He and C. Cheng, "A flying-capacitorclamped five-level inverter based on bridge modular switched-capacitor topology," *IEEE Trans. Ind. Electron.*, vol. 63, no. 12, pp. 7814-7822, Dec. 2016.

- [13] A. Tsunoda, Y. Hinago and H. Koizumi, "A grid connected inverter with switched capacitor inverter using series/parallel conversion," 2012 15th International Power Electronics and Motion Control Conference (EPE/PEMC), 2012, pp. LS7c.4-1-LS7c.4-5, doi: 10.1109/EPEPEMC.2012.6397513.

- [14] Y. Ounejjar, K. Al-Haddad and L. Gregoire, "Packed U Cells Multilevel Converter Topology: Theoretical Study and Experimental Validation," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1294-1306, April 2011.

- [15] K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu and S. Jain, "Multilevel Inverter Topologies With Reduced Device Count: A Review," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 135-151, Jan. 2016.

- [16] M. B. Kalashani and M. Farsadi, "A new switched-capacitors boost inverter for renewable energy sources and POD control modulation," 2014 22nd Iranian Conference on Electrical Engineering (ICEE), 2014, pp. 636-641, doi: 10.1109/IranianCEE.2014.6999618.

- [17] M. F. Kangarlu and E. Babaei, "A generalized cascaded multilevel inverter using series connection of sub-multilevel inverters," *IEEE*

*Trans. Power Electron.*, vol. 28, no. 2, pp. 625-636, Feb. 2013.

- [18] E. Babaei, "A cascade multilevel converter topology with reduced number of switches," *IEEE Trans. Power Electron.*, vol. 23, no. 6, pp. 2657-2664, Nov. 2008.

- [19] K. K. Gupta and S. Jain, "A novel multilevel inverter based on switched DC sources," *IEEE Trans. Ind. Electron.*, vol. 61, no. 7, pp. 3269-3278, July 2014.