# Mathematical Modeling of DC-DC Converter

DURGESH SARANKAR<sup>1</sup>, ASHISH KUMAR SINGHAL<sup>2</sup>

<sup>1,2</sup> Department of Electrical Engineering, Sagar Institute of Science Technology and Eng., Bhopal, India

Abstract -- This is a three-switch converter belongs to fifthorder family and performs boosting operation. A new twoinput Boost-SEPIC DC-DC converter suitable to draw power from two different dc sources feeding a common dcbus is presented in this paper The salient feature of the proposed converter is that both the sources are simultaneously supplying power to the downstream load at reduced ripple current. This feature is particularly attractive for dc grid application.

#### I. INTRODUCTION

The technological development of power electronics definitely brought back dc system in power utilization reliability, accuracy and better load regulation are main issues of modern power supply Today power electronics system are highly developed so demand of Switch-mode power converter is increasing day by day in various application such as hybrid vehicles and telecommunication power supply. In order to utilize maximum energy from more than one energy source such as fuel cell, battery, solar array and wind energy various multi input converter has been proposed in the recent year. Depending upon the applications one could select a feasible topology by considering many features like reliability, cost and flexibility. It is more advantageous to use multi-input converter rather than several independent single source converters as it results in less number of components, more stability in modern power electronics system several power sources such as battery ultra capacitor, fuel cells are used, therefore utilization of multi-input converters is inevitable. Multi input converter has advantage of higher system efficiency, high power density, light weight and small size.

The objective of this paper is to generate a two input topology by using pulsating source cell derived from six non-isolated converter such as buck, boost buckboost, Cuk, SEPIC and Zeta. In this paper one boost pulsating source current cell (PCSC) and one SEPIC

prime PWM converter are combined to transfer power from source to load [1]. The basic idea of this paper is to insert the PCSC into the energy buffer portion of the prime SEPIC converter such that both power source can transfer power to the load simultaneously. Basically any converter (except buck and boost) can be divided in to three section namely input portion IP, energy storing buffer portion EBP, and output portion OP. During one moment of switching cycle input portion will transfer power to the buffer portion and during next moment of switching cycle energy buffer portion will transfer the stored energy to the output portion without consuming any energy. This energy buffer portion may be a voltage or current buffer. There are certain rules to connect PCSC are PVSC with prime PWM converter [1].

To address some the issues various type of multi-input converter with different topology has been already reported in literature. In this paper boost PCSC and SEPIC converter based multi-input converter is proposed and then digital controller have been design to ensure load bus voltage regulation together with distribution of power by appropriate control of input dc power sources. The proposed converter has a unique feature of boosting action which is important from dc grid application point of view. Several controller design approaches have been reported in literature .However depending upon the interaction between the control loops control structure has to be chosen. If the interaction is very small then decentralized control technique will be a feasible option.

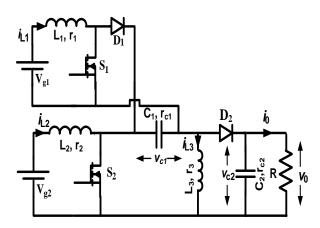

Fig. 1. Two-input dc-dc converter circuit diagram.

Fig. 4. Mode 3

## II. MODELING OF TWO-INPUT DC-DC CONVERTER

The proposed two-input dc-dc converter, shown in Fig. 1, has two different power sources and two switching devices with five energy storage elements and hence it forms a fifth order system. The proposed two input Boost SEPIC converter can perform bucking as well as boosting operation with respect to both the sources. The proposed converter can work in both continuous and discontinuous inductor current mode but in view of higher load power requirement this converter is analyzed for continuous inductor current mode of operation. Different modes of operation depend upon the magnitude of duty ratios. Depending upon the duty ratio three different schemes are possible. Scheme 1: $d_1 > d_2$  Scheme 2:  $d_1 < d_2$  and Scheme 3:  $d_1=d_2$ . In first scheme  $(d_1>d_2)$  The circuit is going to operate under four different modes in one switching cycle .In this paper scheme  $2(d_1 < d_2)$  is considered in which circuit exhibits three mode peration and for scheme 3  $(d_1=d_2)$  only two modes are possible in a switching cycle.

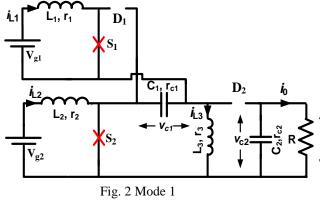

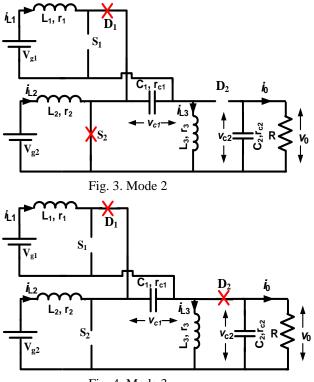

For scheme 2  $(d_2 > d_1)$  assuming switches and diodes are ideal then converter exhibits three mode of operation in a switching cycle .(a) mode- $1:S_1,S_2$  both are ON and diode  $D_1, D_2$  are OFF.(b) mode-2: $S_2, D_1$  are ON and  $S_1, D_2$  are OFF.(c) mode-3: $S_1, S_2$  both are OFF and  $D_1, D_2$  both are ON. During mode-1 inductor  $L_1$ and  $L_2$  are linearly charging by their respective source voltages  $V_{g1}$  and  $V_{g2}$  and capacitor  $C_1$  charges inductor  $L_3$  during this mode load voltage is obtained from capacitor  $C_2$ . In mode-2 inductor  $L_2$  charges linearly but inductor  $L_l$  current will decrease linearly. During this mode of operation energy stored in inductor  $L_{I}$ will transferred to buffer capacitor  $C_1$ . Buffer capacitor will play a very important role in power processing. Depending upon the magnitude of voltage across buffer capacitor direction of power flow will be decided. In mode-3 both switches are in OFF state so both sources will transfer power to the load simultaneously.

Depending on the load demand and available power with each dc source three different cases will arise, which are: (i)  $d_1 > d_2$ , (ii)  $d_1 < d_2$ , (iii)  $d_1 = d_2$ . State space modeling of the converter is required to obtain mathematical model of the physical converter system. For the design of digital control system discrete time modeling is required. In this paper the  $d_1 < d_2$  case is analyzed for the trailing-edge off time synchronized switching signals. If the system is linear and time invariant then for each mode of operation the power stage dynamics can easily be described by a set of state equations in matrix form given by:

$$\dot{x} = A_K x + B_K u$$

$$y = C_k x + F_k u$$

(1)

where  $\begin{bmatrix} x \end{bmatrix} = \begin{bmatrix} i_{L1} & i_{L2} & i_{L3} & v_{c1} & v_{c2} \end{bmatrix}^T$ ,  $\begin{bmatrix} u \end{bmatrix} = \begin{bmatrix} V_{g1} & V_{g2} \end{bmatrix}^T$  and k=1,2,3 for mode-1, mode-2 and 3, respectively.

Applying volt-sec balance to all the inductors mode by mode in a switching cycle gives the voltage across all three inductor and solving equation voltage conversion ratio of this converter can be derived given by equation  $2 V_g = \frac{V_{g2}}{V_{g1}} - \frac{V_{g1}}{V_{g1}}$

(2) equation .2.

$$v_o = \frac{1}{(1-d_2)} = \frac{1}{(1-d_1)}$$

From equation 2. it is clear that the load voltage is dependent on the both input dc sources as well as both switch duty ratio and converter is going to perform boosting operation with respect to both the power source due to this feature this converter is best suited for dc grid application and both input source can be utilize to fulfill load demand.

Table 1. Converter Circuit ElementDesignEquations

The design equation of the circuit element can be obtained from time domain analysis.

| $L_1 = \frac{V_{g1}d_1}{f_s \Delta i_{L1}}$ | $C_1 = \frac{i_{L3}d_1}{f_s \Delta v_{c1}}$      |

|---------------------------------------------|--------------------------------------------------|

| $L_2 = \frac{V_{g2}d_1}{f_s \Delta i_{L2}}$ | $C_2 = \frac{I_0(d_2 - d_1)}{f_s \Delta v_{c2}}$ |

$$L_3 = \frac{V_0(1 - d_1)}{f_s \Delta i_{L3}}$$

For the proposed converter assuming inductor current ripple to be 10% of current and capacitor voltage ripple to be 5% of output voltage. From Table 1.

*L*<sub>1</sub>=312 μH, *L*<sub>2</sub>=513 μH, *L*<sub>3</sub>=702 μH

$C_1=27 \ \mu F, \ C_2=60 \ \mu F.$

From equation 1 system matrices in the corresponding mode can be written as,

$$A_{1} = \begin{bmatrix} -\frac{r_{1}}{L_{1}} & 0 & 0 & 0 & 0 \\ 0 & -\frac{r_{1}}{L_{2}} & 0 & 0 & 0 \\ 0 & 0 & -\left(\frac{r_{n}+r_{1}}{L_{2}}\right) & \frac{1}{L_{2}} & 0 \\ 0 & 0 & -\frac{1}{C_{1}} & 0 & 0 \\ 0 & 0 & 0 & 0 & -\left(\frac{1}{C_{2}(r_{2}+R)}\right) \end{bmatrix}$$

(3a)

$$P_{1} = P_{2} = P_{3} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 \end{bmatrix}$$

(3b)

$$E_{1} = \begin{bmatrix} 0 & 0 & 0 & 0 & \frac{R}{R+re_{2}} \end{bmatrix}$$

(3c)

$$F_{1} = F_{2} = F_{3} = \begin{bmatrix} 0 \end{bmatrix}$$

(3d)

$$B_{1} = B_{2} = B_{3} = \begin{bmatrix} \frac{1}{L_{1}} & 0 & 0 & 0 & 0 \\ 0 & \frac{1}{L_{2}} & 0 & 0 & 0 \end{bmatrix}^{T}$$

(3e)

$$A_{2} = \begin{bmatrix} -\left[\frac{r_{1}+r_{2}}{L_{1}}\right] & 0 & \frac{r_{2}}{L_{2}} & -\frac{1}{L_{2}} & 0 \\ 0 & -\frac{r_{2}}{L_{2}} & 0 & 0 & 0 \\ \frac{r_{0}}{L_{0}} & 0 & -\frac{r_{1}+r_{3}}{L_{3}} & \frac{1}{L_{3}} & 0 \\ \frac{1}{C_{1}} & 0 & -\frac{r_{1}+r_{3}}{L_{3}} & \frac{1}{L_{3}} & 0 \\ 0 & 0 & 0 & 0 & -\left(\frac{1}{C_{2}(r_{2}+R)}\right) \end{bmatrix}$$

(3f)

$$E_2 = \begin{bmatrix} 0 & 0 & 0 & \left(\frac{R}{R+r_{c2}}\right) \end{bmatrix}$$

(3g)

$$A_3 =$$

$$\begin{vmatrix} -\left(\frac{r_{1}+r_{c1}}{L_{1}}\right) & -\left(\frac{r_{c1}}{L_{1}}\right) & 0 & -\frac{1}{L_{1}} & 0 \\ -\frac{r_{c1}}{L_{2}} & -\frac{R_{p}}{L_{2}} & -\frac{R_{e}r_{c2}}{L_{2}} & -\frac{1}{L_{2}} & -\frac{R_{e}}{L_{2}} \\ 0 & -\frac{R_{e}r_{c2}}{L_{3}} & -\frac{1}{L_{3}}\left(r_{3}+R_{e}r_{c2}\right) & 0 & -\frac{R_{e}}{L_{3}} \\ \frac{1}{C_{1}} & \frac{1}{C_{1}} & 0 & 0 & 0 \\ 0 & \frac{R_{e}}{C_{2}} & \frac{R_{e}}{C_{2}} & 0 & -\left(\frac{R_{m}}{C_{2}}\right) \end{vmatrix}$$

Where,

$$R_{e} = \frac{R}{R + r_{e2}} R_{m} = \frac{1}{R + r_{e2}} R_{p} = r_{2} + r_{e1} + R_{e} r_{e2}$$

$$E_{3} = \begin{bmatrix} 0 & \frac{Rr_{c2}}{(R + r_{c2})} & \frac{Rr_{c2}}{(R + r_{c2})} & 0 & \frac{R}{(R + r_{c2})} \end{bmatrix}$$

(3j)

The small-signal discrete-time model [4] can be written as:

$$\hat{x}[n] = \phi \hat{x}[n-1] + \gamma_1 \hat{d}_1[n-1] + \gamma_2 \hat{d}_2[n-1]$$

(4)

The output state-space equation can be written as follows:

$$\hat{y}[n] = E_i \hat{x}[n]. \tag{5}$$

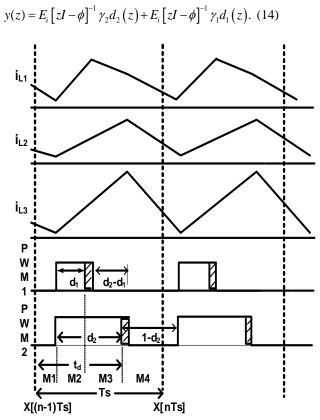

In dc-dc converters discrete time modeling can be easily established for trailing edge and leading edge modulation In this paper, trailing-edge OFF-time sampling with a sampling frequency  $f_s(=1/T_s)$ , as shown in Fig. 5, is implemented. In trialling edge off time sampling the signal is sensed during off time, and the PWM pulses are aligned at the beginning of the pulse. The mathematical analysis is discussed in the following paragraphs. From Fig. 2 in interval-1,  $(n-1)T_s <1 < [(n-1)T_s + t_d - d_1T_s]$  the system state equation can easily be written as

$$\dot{x} = A_3 x$$

(6)

Assuming the source voltage is almost constant during each mode of operation of the switching cycle, the discrete-time model with state ' $x[(n-1)T_s]$ ' at the beginning [4] and duty ratio 'd' can easily be defined by

$$x\left[\left(\mathbf{n}-1\right)T_{s}+t_{d}-d_{1}T_{s}\right]=e^{A_{3}\left(t_{d}-d_{1}T_{s}\right)}x\left[\left(n-1\right)T_{s}\right]$$

(7)

Along similar lines, the discrete-time models for the remaining time intervals are established as

Interval-2:

$$\left[ (\mathbf{n}-1)T_s + t_d - d_1T_s \right] < t < \left[ (\mathbf{n}-1)T_s + t_d \right]$$

$x \left[ (\mathbf{n}-1)T_s + t_d \right] = e^{A_1 \left[ d_1T_s \right]} e^{A_3 \left( t_d - d_1T_s \right)} x \left[ (n-1)T_s + t_d - d_1T_s \right]$

(8)

Interval-3:

$$[(n-1)T_s + t_d] < t < [(n-1)T_s + t_d + (d_2T_s - d_1T_s)]$$

$x[(n-1)T_s + td + (d_2T_s - d_1T_s)]$

$= e^{A_2[d_2T_s - d_1T_s]} e^{A_1d_1T_s} e^{A_3(t_d - d_1T_s)} x[(n-1)T_s] + K_1T_s e^{A_2T_s[d_2 - d_1]} \hat{d}_1 (n-1)$

(9)

Interval 4:

$$[(n-1)T_s + t_d + (d_2T_s - d_1T_s)] < t < [nT_s]$$

$x[nT] = e^{A_s[T_s - d_2T_s - t_d + d_1T_s]}e^{A_s[t_d - d_1T_s]}e^{A_2T_s(d_2 - d_1)}e^{A_td_1T_s}x[(n-1)T]$

$$K[nI_{s}] = e^{A_{s}[T_{s}-d_{2}T_{s}-t_{d}+d_{l}T_{s}]}e^{A_{2}T_{s}[d_{2}-d_{l}]}\hat{d}_{1}(n-1)$$

$$+K_{2}T_{s}e^{A_{3}[T_{s}-d_{2}T_{s}-t_{d}+d_{l}T_{s}]}\hat{d}_{2}(n-1)$$

(10)

The small-signal discrete-time model in standard form for the converter under discussion can be written as:

$$\hat{x}[nT_s] = \phi \hat{x}[(n-1)T_s] + \gamma_2 \hat{d}_2[(n-1)T_s] + \gamma_1 \hat{d}_1[(n-1)T_s]$$

(11)

Comparing eqns. (10) & (11), it is easy to obtain

$$\phi = e^{AT_s}, \quad \gamma_1 = K_1 T_s e^{A_3 [T_s - d_2 T_s - t_d + d_1 T_s]} e^{A_2 T_s [d_2 - d_1]}$$

$$\gamma_2 = K_2 T_s e^{A_3 [T_s - d_2 T_s - t_d + d_1 T_s]}$$

$$K_1 = \left[ (A_1 - A_2) x + (B_1 - B_2) U \right]$$

$$K_2 = \left[ (A_2 - A_3) x + (B_2 - B_3) U \right].$$

Taking the z-transform of eqn. (11),

$$x(z) = [zI - \phi]^{-1} [\gamma_1 d_1(z) + \gamma_2 d_2(z)]$$

(12)

Taking the z-transform of equation (8) results in

$y(z) = E_i x(z)$ (13)

Combining eqns. (9) and (10) results in

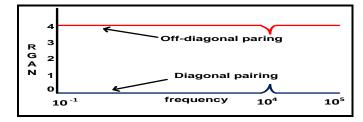

### III. APPLICATION OF RGA THEORY TO CONVERTER

To design the controller for two input converter we need to know the degree of interaction between the control loops. The most popular method of interaction analysis is Relative Gain Array RGA .From this analysis we can decide the best suited control signal to control output voltage and source current. RGA is the ratio of open loop gain to closed loop gain. For the proposed converter interaction is less so decentralized controller is preferred. Expression of RGA may be defined as.

$$\wedge (G) = G(0) \cdot (G(0)^{-1})^T$$

(15)

Fig. 6.RGAN v/s frequency plot

$$RGA = \begin{bmatrix} 1.0004 & -0.0004 \\ -0.0004 & 1.0004 \end{bmatrix}$$

### IV. SIMULATION STUDIES AND EXPERIMENTAL RESULTS

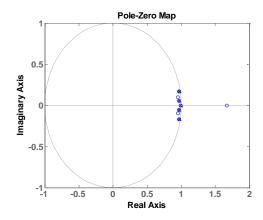

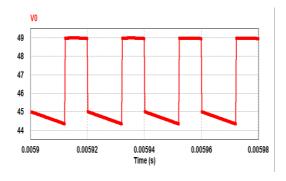

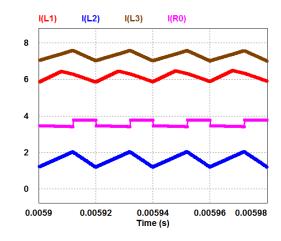

To study the salient features of proposed two input DC-DC converter and to verify the dc bus regulation together with the load distribution capability a 48 V, 177 Watts converter is considered. In this converter DC source-1 is a low voltage source and DC source -2 is considered as high voltage source. The parameters of the converter element is shown in Table-I. For the parameters given by Table 1 transfer functions of this converter are.

$$G_{11}(z) = \frac{-1.05z^4 + 4.829z^3 - 8.173z^2 + 6.08z - 1.685}{den}$$

Fig. 5. PWM gating signals and Off-Time sampling process.

## © MAR 2018 | IRE Journals | Volume 1 Issue 9 | ISSN: 2456-8880

$$G_{12}(z) = \frac{0.3685z^4 - 1.24z^3 + 1.528z^2 - 0.8085z + 0.1522}{den}$$

$$G_{22}(z) = \frac{2.393z^4 - 9.236z^3 + 13.4z^2 - 8.657z + 2.103}{den}$$

$$den = z^5 - 4.883z^4 + 9.567z^3 - 9.403z^2 + 4.636z - 0.9172$$

(16)

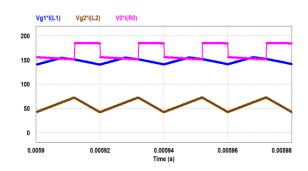

For this converter PSIM is used for simulation purpose steady state voltage and inductor current waveform are shown in figure 8 and 9 respectively .Load shared by each source is show in figure 10.

Fig. 7Polee zero plot of the transfer function (G)

Fig. 8.steady state waveform of load voltage

Fig. 9.steady state waveform of inductor and load current

Fig. 10 .Load power distribution

#### V. CONCLUSION

A new two input boosting DC-DC converter for dc grid application is proposed in this paper. State space and discrete time modeling have been performed for different mode of operation, Simulation results were in agreement with theoretical studies.

#### REFERENCES

- Y.C.Liu and Y.M.Chen, "A systemic approach to synthesizing multi-input dc-dc converter "IEEE Tran.Power Electron.vol,24,no.1,pp.116-127,Jan.2009.

- [2] M. Veerachary, "Two-loop controlled buck-SEPIC converter for input source power management," IEEE Trans. On Industrial Electronics, Vol. 59(11), pp. 4075-4087, 2012.

- [3] D. Maksimovic and R. Zane, "Small-Signal Discrete Time Modeling of Digitally Controlled PWM Converters", IEEE Trans.

on Power Electronics, vol. 22, no. 6, pp. 2552-2556, Jun. 2007.

- [4] Veerachary. Mummadi, Ramakanth Naidu Gowra, and Dileep Ganta. "Discrete-time modeling of multi-state DC-DC converters."Proc. of IEEE conference on Power Electronics, Drives and Energy Systems (PEDES) & Power India, 2010, pp. 1-6.

- [5] K. P. Yalamanchili, M. Ferdowsi, Keith Corzine, "New Double input dc-dc converters for automotive applications", IEEE Applied Power Electronics Conference (APEC), 2006, CD-ROM proceedings.

- [6] Y.-M. Chen, Y.-C. Liu, and S.-H. Lin, "Double-input PWM dc/dc converter for high/low voltage sources," in Proc. INTELEC, 2003, pp. 27–32.

- [7] A. Khaligh, J. Cao, and Y. J. Lee, "A multiple-input DC–DC converter topology," IEEE Trans. Power Electron., vol. 24, no. 3, pp. 862–868, Mar. 2009.

- [8] MATLAB user manual, 2009.

- [9] PSIM, user manual, 2007.

- [10] M. Veerachary, "Robust stabilizing Digital Controller for Soft- Switching zero voltage turn-on H- bridge Boost Converter," IEEE Trans. Ind. Electron., vol. 58, no.7, 2011, pp.2883- 2897.

- [11] G. Hua, F.C. Lee, "A new class of zero voltage- switched PWM converters," High frequency Power Conversion Conf Proc., 1994, pp. 637-643.

- [12] G. Hua, Yiming Jiang, F.C. Lee, "Analysis, design, and experiments of ZVT-PWM boost converter," published in Virginia Power Electronic Center (WEC) Seminar, 1992, pp. 213-219.

- [13] M. Veerachary, "Two input DC-DC Converter for DC grid applications", IEEE Power India Conference, 2012, pp. 21-26.

- [14] R.W.Erickson and D.Maksimovic, "Fundamentals of Power Electronics," second edition, Springer International Edition, 2006.