# Design of Fault Tolerance Parallel FFT's Using Xilinx 14.5v

N. RAJ KUMAR<sup>1</sup>, KAMBLE SHIVDAYAL<sup>2</sup>

<sup>1, 2</sup> ECE Department, Matrusri Engineering College, Hyderabad, India

Abstract- Soft errors stance a dependability threat to modern-day electronic circuits. This makes defense against soft errors a requirement for several applications. Communications along with signal handling systems are no exemptions to this pattern. To maintain the reliability of the complex systems few techniques have been proposed. For some applications, a remarkable option is to utilize algorithmic based blunder resistance (ABFT) methods that attempt to exploit the algorithmic household or business homes to identify as well as proper errors. Signal handling along with communication applications are well matched for ABFT. One circumstance is Fast Fourier Transforms (FFTs) that are a key structure in many systems. There are various protection schemes to identify and ad-just errors in FFTs. It is normal to discover various blocks are working in parallel. Recently; a new method is exploiting to implement a blame tolerance in parallel. In this brief, this technique is first applied to protect FFTs. Then, two improved protection schemes that combine the use of error correction codes and Parseval checks are proposed and evaluated. The results show that the proposed schemes can further reduce the implementation cost of protection.

Indexed Terms- Error correction codes (ECCs), Fast Fourier Transforms (FFTs), soft errors.

## I. INTRODUCTION

Nowadays, the complexity of interactions as well as signal handling circuits enhances yearly. The CMOS modern technology scaling has actually made today's layouts extra vulnerable to radiation generated soft errors. Soft error can modify the sensible output of a circuit node producing a mistake that influences the system performance and issue comes to be more intricacy of the soft error price significantly increases keeping that of circuits scaling. At the same time, the

scaling shows that transistors run with decreased voltages as well as are far more prone to errors caused by sound and also manufacturing variations. The importance of radiation-induced soft errors furthermore increases as modern technology scales. To guarantee that soft errors do not impact the procedure of a provided circuit, a vast array of approaches can be used. These includes Specifically establishing collections made use of for complicated circuit and also customized manufacturing procedure such as the silicon on insulator design additionally made use of for lowering the mistake possibility. Another alternative is to make standard circuit blocks or total layout libraries to reduce the likelihood of soft blunders. Finally, it is furthermore possible to consist of redundancy at the system degree to discover and additionally correct mistakes. For example, making use of duplication using decreased accuracy copies of the filter has actually been proposed as an option to Triple Modular Redundancy (TMR) nevertheless with a reduced expense. The knowledge of the distribution of the filter result has also been just recently exploited to find as well as additionally proper errors with lowered expenditures. This is frequently described as algorithm-based Fault Tolerance (ABFT). This strategy can lower the overhead called for to shield a circuit. Signal handling in addition to interactions circuits are well matched for ABFT as they have regular structures along with numerous mathematical residential properties. Throughout the years, great deals of ABFT techniques have been recommended to secure the standard obstructs that are regularly used in those circuits. Signal handling along with communication applications are well matched for ABFT. One circumstance is quick Fourier changes (FFTs) that are a key structure in many systems. Quick Fourier Modification Rapid Fourier Transform (FFT) formula transforms a signal from time domain into a collection in the uniformity domain. Rapid Fourier transforms are widely utilized for lots of applications that consist of design, scientific research, in addition

to math. It computes improvements with DFT matrix. The FFT treatment starts with decomposing N-point time domain signal and additionally computing N uniformity ranges as well as finally creating a single range. The Discrete Fourier Transform (DFT) Discrete Fourier Transform (DFT) is an important device in a number of interaction applications like OFDM, and so on. DFT is similarly gauged as one of the devices to act upon frequency evaluation of discrete time signals.

$$X(k) = \sum_{n=0}^{N-1} x(n)e^{-\frac{\sqrt{2\pi k n}}{N}}, n = 0, 1, \dots, N-1$$

In digital signal processing, fast Fourier transform plays a major role which increases the computing efficiency for obtaining large discrete Fourier transform (DFT). At recently a new technique is proposed which is based on Error -Correction codes (ECCs). The idea behind in this method, each filter must be equivalent of a bit in ECC and parity check bits it can be calculated by using addition. The output of the sum of various inputs is the sum of the single outputs; this technique is used for operations. A number of protection schemes have been suggested to detect and additionally proper mistakes in FFTs. Among those, perhaps making uses of the parseval checks or sum of squares examine is one of the most thoroughly understood. In contemporary communication systems, it is progressively typical to locate a number of blocks running in parallel. Lately, a strategy that manipulates this fact to accomplish fault resistance on identical filters has actually been proposed. In this short, this technique is very initial put on safeguard FFTs. After that, 2 improved protection plans that incorporate making use of mistake adjustment codes as well additionally Parseval checks are recommended as well as likewise examined. At any time, it is considered that there can only be a single fault on the system. There are three fundamental principles are offering. They is:

- 1) The estimation of the ECC method for the secure of parallel FFTs displays its function in terms of overhead and protection effectiveness.

- 2) Another methods which is based on the use of Parseval checks or sum of Squares (SOSs) checks merged with the redundant (parity) FFT.

- 3) The proposition of both methods on which the ECC is utilized on the SOS checks rather than on

the FFTs. The proposition of two methods produce a new approaches to secure parallel FFTs that can be more area efficient than compare to single FFTs independently. The end results reveal that the recommended systems can much better reduce the execution cost of defense. The suggested design of this paper analysis the reasoning dimension, location as well as power usage using Xilinx 14.5.

## II. METHODOLOGIES

In the existing methods, signal processing and communication are well suited for Algorithmic Based Fault Tolerant (ABFT) as they have regular structures and many algorithmic properties. Over the years, many ABFT techniques have been proposed to protect the basic blocks that are commonly in those circuits. Several works have considered the protection of digital filters. In parallel FFT protection using ECCs method, error correction codes (ECCs) has been used to detect and correct the error. In this techniques, each FFT can be the equivalent of a bit in an ECC and parity check bits can be computed.Using addition. This technique can be used for operation, in which the output of the sum of several inputs is the sum of the individual outputs. In parity-SOS (first technique) fault-tolerant parallel FFTs method, Parseval check is used to detect the errors in individual FFT and only one redundant FFT is enough to correct the error. So that area and power consumption of this method is less compared to existing method. The proposed techniques provide new alternatives to protect parallel FFTs that can be more efficient than protecting of the FFTs independently, In Parity-SOS-ECC (second technique) fault-tolerance parallel FFTs method, Parseval check is used to detect and correct the errors. The main advantage of this method is number of parseval check is less compared with first method. So, this method is more effective compared with first method. In this method, we are using parseval check method to detect the errors in the original module. By using this method we able to detect more than one error in the original module. After that errors in the original modules are corrected by using ECC.

#### III. CONTRIBUTION

The aim of the project is to design techniques to reduce the implementation cost of protection and low complexity and the protection against soft errors. Error detection and correction is to add some redundancy (i.e., some extra data) to a message, which receivers can use to check consistency of the delivered message, and to recover data determined to be corrupted. Errordetection and correction schemes can be either systematic or non-systematic: In a systematic scheme, the transmitter sends the original data, and attaches a fixed number of check bits (or parity data), which are derived from the data bits by some deterministic algorithm. If only error detection is required, a receiver can simply apply the same algorithm to the received data bits and compare its output with the received check bits; if the values do not match, an error has occurred at some point during the transmission. In a system that uses a non-systematic code, the original message is transformed into an encoded message that has at least as many bits as the original message. Two techniques are proposed and evaluated the error correction rate. The first technique is based on merge an ECCs and with traditional SOS check. The SOS check is used to identify the errors and finds the location of errors, finally parity FFT is used for error correction. The detection and location of errors can be completed using SOS check per FFT otherwise using a set of SOS checks that form an ECC. The proposed techniques calculate both in terms of implementation density and error detection capabilities. The second technique, which consisting of a parity FFT and set of SOS checks that form the ECC. Result of the second technique provides the better implementation complexity.

# IV. LITERATURE SURVEY

M. Nicolaidis, "in nano metric applied sciences, intersections have been more and more responsive several types of imbalances. Delicate mistakes, your difficulty in place of house programs inside the past, were your security trouble situated at little. molecules together with hazy unpaired electrons result in single-event shocks (SEU), stirring cells, presses, moreover boot, moreover single-event wanderer (set), proposed that in connectional good judgment together with detected all spins as a consequence loafer linked for - the components about classification. To stand the one in question predicament, the clothier ought to govern that variety containing smooth transgression cure strategies adjusted to varied district systems, make

sensors, together with make boundaries. Smart this one card, without help construe diversified mestre along with name remission strategies which could assistance spectacular dressmaker reaches even her own about nod objectives.

A. L. N. Reddy and P. Banerjee, The increasing demands for high-performance signal processing along with the availability of inexpensive highperformance processors have results in numerous proposals for special-purpose array processors for signal processing applications. A functional-level concurrent error-detection scheme is presented for such VLSI signal processing architectures as those proposed for the FFT and QR factorization. Some basic properties involved in such computations are used to check the correctness of the computed output values. This fault-detection scheme is shown to be applicable to a class of problems rather than a particular problem, unlike the earlier algorithm-based The effects error-detection techniques. of roundoff/truncation errors due to finite-precision arithmetic are evaluated. It is shown that the error coverage is high with large word sizes.

S. Pontarelli, G. C. Cardarilli, M. Re, and A. Salsano, the design of a finite impulse response (FIR) filter with fault tolerant capabilities based on the residue number system is analyzed. Differently from other approaches that use RNS, the filter implementation is fault tolerant not only with respect to a fault inside the RNS moduli, but also in the reverse converter. An architecture allowing fault masking in the overall RNS FIR filter is presented. It avoids the use of a trivial triple modular redundancy (TMR) to protect the blocks that performs the final stages of the RNS based FIR computation.

T. Hitana and A. K. Deb, maintaining high reliability in fault detection is a prominent concern in case of life critical missions. In this paper, we describe how the invariant-based technique has been improved and extended. It is shown that the detection time latency can be considerably reduced. In order to widen the fault coverage and fully control the detection time, a cost effective non-concurrent error detection scheme is proposed. The results indicate that, for any specified checking period, 100% non-concurrent error detection is possible.

# V. EXISTING SYSTEM

The main objective of fault tolerant is to secure the parallel FFTs from errors. Different protection techniques have been proposed for error recognization and identification in FFTs.

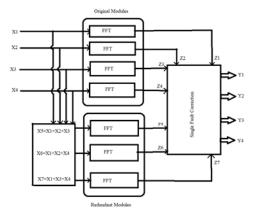

Fig1: Parallel protection FFT's using ECC

In digital filters a new-protection method is used which is based on the use of ECCs. This technique is shown in Fig.1. For case, the basic and simple method is error correction hamming codes is used. Redundant (parity) bit is used to detect errors which are used to perform XOR operation with the data bits.

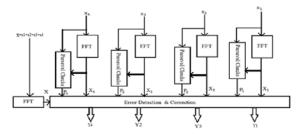

Fig. 2: Parity-SOS Fault Tolerant Parallel FFT

In this technique, it consists of four FFT modules with inputs x1, x2, x3 & x4 and outputs X1, X2, X3 & X4 and also parity (redundant) FFT is addition of all original FFT inputs. SOS check is merged with the ECC.SOS check is used on each FFT to detect mistakes .suppose an fault is detected ,the output of the parity FFT is used to correct that errors and ECC is used to correct that mis-takes. For example an error is detected using P1, P2, P3 & P4 and it can be corrected by rebuild the FFT with fault. By utilizing the parity FFT(X) output and the remaining FFT outputs.

#### VI. PROPOSED SYSTEM

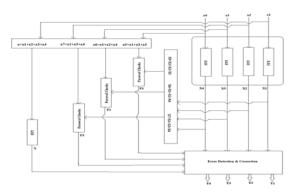

Parity-SOS-ECC Fault tolerant parallel FFT is a technique which is combined with SOS check and ECC replace by using an SOS check per FFT .Parity-SOS is used to detect an error and ECC part is used to correct that mistake. In this technique, the advantage of the first Parity-SOS technique is minimizing the SOS checks. The advantages of these two techniques are minimizing the number of SOS checks needed. In this technique, it contains four FFT original modules with inputs x1,x2,x3 & x4 and outputsX1,X2,X3 & X4 as shown in fig.3 .The x5,x6,x7 and X5,X6,X7 are the inputs to the parseval check and it used to perform XOR operation with the inputs and outputs of the original FFTs. Parseval check is used to compare the both inputs , if we are getting same outputs then it is represented as a no error. Suppose, if we are detect an error in X1 then the inputs to the parseval check performs comparison if it is not equal then it is represented as an error in the module .An Parity-FFT is used to correct that error .

Fig 3: Parity-SOS-ECC fault tolerant parallel FFT's

In this second technique it minimizes the number of SOS checks. A final observation is that the ECC scheme can detect all errors that exceed a given threshold (given by the quantization used to implement the FFTs).

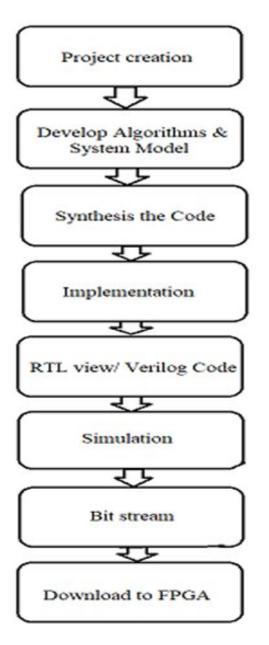

Implementation through Xilinx 14.5: It requires Xilinx ISE 14.5 version of software where Verilog source code can be used for design implementation. This tool can be used to create, implement, simulate, and synthesize Verilog designs for implementation on FPGA chips.A Verilog model is translated into the "gates and wires" that are mapped onto a programmable logic device such as a CPLD or FPGA, and then it is the actual hardware being configured, rather than the Verilog code being executed as if on some form of a processor chip.

Fig 4: Design flow of Xilinx Implementation

# VII. RESULT

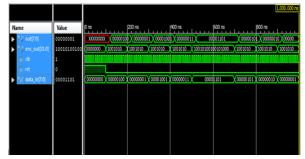

The Results for the protection Schemes, In this work, parallel FFT and then secured methods are merged that the use of error correction codes (ECCs) and parseval checks are used to detect and correct a single bit fault. Simulation and Synthesis report for FFT using ECC, SOS, ECC-SOS, obtained in Xilinx software 14.5v.

Fig.5: Simulation Results for Parity-SOS-ECC Fault Tolerant Parallel FFT's Fault and Corrected Output.

## CONCLUSION

The protection of parallel FFTs implementation against soft errors. The main benefit over the first parity-SOS scheme is to reduce the number of SOS checks needed. The proposed techniques have been evaluated both in terms of implementation complexity and error detection capabilities.

#### FUTURE SCOPE

In this method, It uses the three schemes for the protection of FFT which is able to detect up to two faults and correct only single fault. By making the 4-point FFT with the input bit length 32 to the Parallel FFT protection, Parity-SOS fault tolerance parallel FFT's, Parity SOS-ECC techniques for Multi bit faults by using trellis code can reduce the area, power & delay is analyzed by using cadence report 90nm & 180nm technology.

### REFERENCES

[1] N. Kanekawa, E. H. Ibe, T. Suga, and Y. Uematsu, Dependability in Electronic Systems: Mitigation of Hardware Failures, Soft Errors, and Electro-Magnetic Disturbances. New York, NY, USA: Springer-Verlag, 2010.

- [2] R. Baumann, "Soft errors in advanced computer systems," *IEEE Des.Test Comput.*, vol.22, no. 3, pp. 258–266, May/Jun. 2005.

- [3] M. Nicolaidis, "Design for soft error mitigation," *IEEE Trans. Device Mater. Rel.*, vol.no. 3, pp. 405–418, Sep. 2005.

- [4] A. L. N. Reddy and P. Banerjee, "Algorithmbased fault detection for signal processing applications," *IEEE Trans. Computer.*, vol. 39, no. 10, pp. 1304–1308, Oct. 1990.

- [5] T. Hitana and A. K. Deb, "Bridging concurrent and non-concurrent error detection in FIR filters," in *Proc. Norchip Conf.*, Nov. 2004, pp. 75–78.

- [6] S. Pontarelli, G. C. Cardarilli, M. Re, and A. Salsano, "Totally fault tolerant RNS based FIR filters," in *Proc. 14th IEEE Int. On-Line Test Symp. (IOLTS)*, Jul. 2008, pp. 192 194.

- B. Shim and N. R. Shanbhag, "Energy-efficient soft error-tolerant digital signal process" *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 14, no. 4, pp. 336–348, Apr. 2006

- [8] E. P. Kim and N. R. Shanbhag, "Soft N-modular redundancy," *IEEE Trans. Comput.*, vol 61, no. 3, pp. 323–336, Mar. 2012.

- [9] J. Y. Jou and J. A. Abraham, "Fault-tolerant FFT networks," *IEEE Trans. Comput.*, vol. 37, no. 5, pp. 548–561, May 1988.

- [10] S.-J. Wang and N. K. Jha, "Algorithm-based fault tolerance for FFT networks," *IEEE Trans. Comput.*, vol. 43, no. 7, pp. 849–854, Jul. 1994.

- [11] P. P. Vaidyanathanm, Multirate Systems and Filter Banks.Englewood Cliffs, NJ, USA: Prentice-Hall, 1993.

- [12] A. Sibille, C. Oestges, and A. Zanella, MIMO: From Theory to Implementation. San Francisco, CA, USA: Academic, 2010.

- [13] G. L. Stüber, J. R. Barry, S. W. McLaughlin, Y. Li, M. A. Ingram, and T. G. Pratt, "Broadband MIMO-OFDM wireless communications," *Proc.IEEE*, vol. 92, no. 2, pp. 271–294, Feb. 2004.

- [14] S. Sesia, I. Toufik, and M. Baker, *LTE—The UMTS Long Term Evolution: From Theory* to *Practice*, 2nd ed. New York, NY, USA: Wiley,Jul. 2011.

- [15] M. Ergen, Mobile Broadband—Including WiMAX and LTE. New York, NY, USA: Springer-Verlag, 2009.

- [16] P. Reviriego, S. Pontarelli, C. J. Bleakley, and J. A. Maestro, "Area efficient concurrent error detection and correction for parallel filters," *IET Electron. Lett.*, vol. 48, no. 20, pp.1258–1260, Sep. 2012.

- [17] Z. Gao *et al.*, "Fault tolerant parallel filters based on error correction codes," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 23, no. 2, pp. 384–387, Feb. 2015.

- [18] R. W. Hamming,"Error detecting and error correcting codes," *Bell Syst. Tech. J.*, vol. 29 no. 2, pp. 147–160, Apr. 1950.